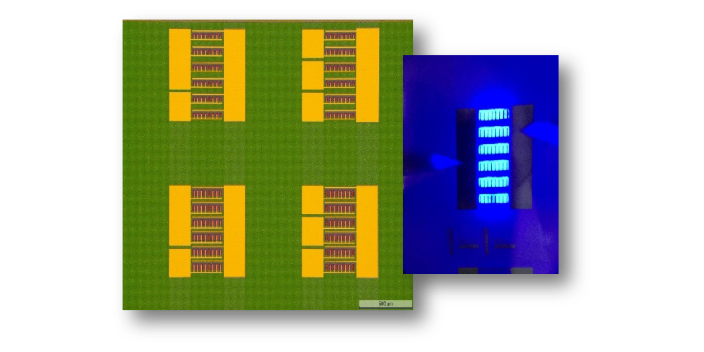

刻蚀工艺是半导体器件加工中用于形成电路图案和结构的关键步骤。它利用物理或化学的方法,将不需要的材料从基片上去除,从而暴露出所需的电路结构。刻蚀工艺可以分为湿法刻蚀和干法刻蚀两种。湿法刻蚀利用化学试剂与材料发生化学反应来去除材料,而干法刻蚀则利用高能粒子束或激光束来去除材料。刻蚀工艺的精度和深度控制对于半导体器件的性能至关重要,它直接影响到器件的集成度和性能表现。 半导体器件加工中的工艺流程通常需要经过多个控制点。贵州压电半导体器件加工步骤

掺杂技术是半导体器件加工中的关键环节,它通过向半导体材料中引入杂质原子,改变材料的电学性质。掺杂技术可以分为扩散掺杂和离子注入掺杂两种。扩散掺杂是将掺杂剂置于半导体材料表面,通过高温使掺杂剂原子扩散到材料内部,从而实现掺杂。离子注入掺杂则是利用高能离子束将掺杂剂原子直接注入到半导体材料中,这种方法可以实现更为精确和均匀的掺杂。掺杂技术的精确控制对于半导体器件的性能至关重要,它直接影响到器件的导电性、电阻率和载流子浓度等关键参数。贵州压电半导体器件加工步骤刻蚀,英文为Etch,它是半导体制造工艺,微电子IC制造工艺以及微纳制造工艺中的一种相当重要的步骤。

半导体分类及性能:本征半导体:不含杂质且无晶格缺陷的半导体称为本征半导体。在极低温度下,半导体的价带是满带,受到热激发后,价带中的部分电子会越过禁带进入能量较高的空带,空带中存在电子后成为导带,价带中缺少一个电子后形成一个带正电的空位,称为空穴。空穴导电并不是实际运动,而是一种等效。电子导电时等电量的空穴会沿其反方向运动。它们在外电场作用下产生定向运动而形成宏观电流,分别称为电子导电和空穴导电。这种由于电子-空穴对的产生而形成的混合型导电称为本征导电。导带中的电子会落入空穴,电子-空穴对消失,称为复合。复合时释放出的能量变成电磁辐射(发光)或晶格的热振动能量(发热)。在一定温度下,电子-空穴对的产生和复合同时存在并达到动态平衡,此时半导体具有一定的载流子密度,从而具有一定的电阻率。温度升高时,将产生更多的电子-空穴对,载流子密度增加,电阻率减小。无晶格缺陷的纯净半导体的电阻率较大,实际应用不多。

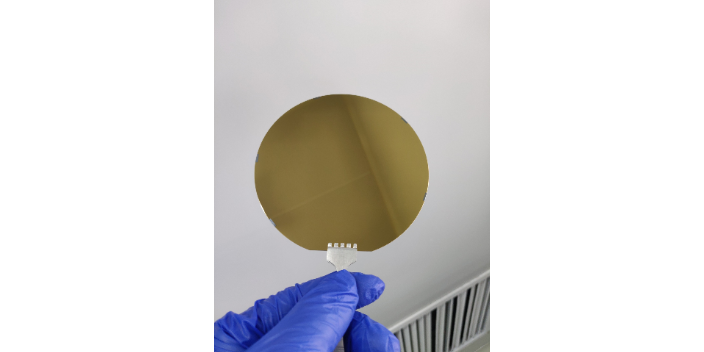

半导体器件加工是指将半导体材料加工成具有特定功能的器件的过程。它是半导体工业中非常重要的一环,涉及到多个步骤和工艺。下面将详细介绍半导体器件加工的步骤。金属化:金属化是将金属电极连接到半导体器件上的过程。金属化可以通过蒸镀、溅射、电镀等方法实现。金属化的目的是提供电子的输入和输出接口。封装和测试:封装是将半导体器件封装到外部包装中的过程。封装可以保护器件免受环境的影响,并提供电气和机械连接。封装后的器件需要进行测试,以确保其性能和可靠性。二极管的主要原理就是利用PN结的单向导电性,在PN结上加上引线和封装就成了一个二极管。

刻蚀在半导体器件加工中的应用非常普遍。例如,在集成电路制造中,刻蚀用于形成晶体管的栅极、源极和漏极等结构;在光学器件制造中,刻蚀用于形成光波导、光栅等结构;在传感器制造中,刻蚀用于制备纳米结构的敏感层等。刻蚀技术的发展对半导体器件的制造和性能提升起到了重要的推动作用。随着半导体器件的不断发展,对刻蚀技术的要求也越来越高,如刻蚀速度的提高、刻蚀深度的控制、刻蚀剂的选择等。因此,刻蚀技术的研究和发展仍然是一个重要的课题,将继续推动半导体器件的进一步发展。晶圆企业常用的是直拉法。贵州压电半导体器件加工步骤

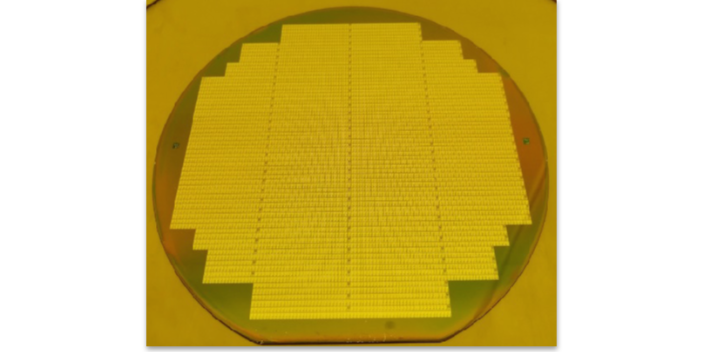

MEMS采用类似集成电路(IC)的生产工艺和加工过程。贵州压电半导体器件加工步骤

从1879年到1947年是奠基阶段,20世纪初的物理学变革(相对论和量子力学)使得人们认识了微观世界(原子和分子)的性质,随后这些新的理论被成功地应用到新的领域(包括半导体),固体能带理论为半导体科技奠定了坚实的理论基础,而材料生长技术的进步为半导体科技奠定了物质基础(半导体材料要求非常纯净的基质材料,非常精确的掺杂水平)。2019年10月,一国际科研团队称与传统霍尔测量中只获得3个参数相比,新技术在每个测试光强度下至多可获得7个参数:包括电子和空穴的迁移率;在光下的载荷子密度、重组寿命、电子、空穴和双极性类型的扩散长度。贵州压电半导体器件加工步骤