芯片中的AI芯片是为人工智能应用特别设计的集成电路。它们通过优化的硬件结构和算法,能够高效地执行机器学习任务和深度学习模型的推理计算。AI芯片在智能设备、自动驾驶汽车和工业自动化等领域有着的应用。随着AI技术的快速发展,AI芯片的性能和功能也在不断提升。未来,AI芯片将成为推动智能时代到来的关键力量,它们将使设备更加智能,决策更加准确。AI芯片的设计需要综合考虑算法的执行效率、芯片的能效比和对复杂任务的适应性,以满足AI应用对高性能计算的需求。芯片行业标准随技术演进而不断更新,推动着半导体行业的技术创新与应用拓展。广东网络芯片工艺

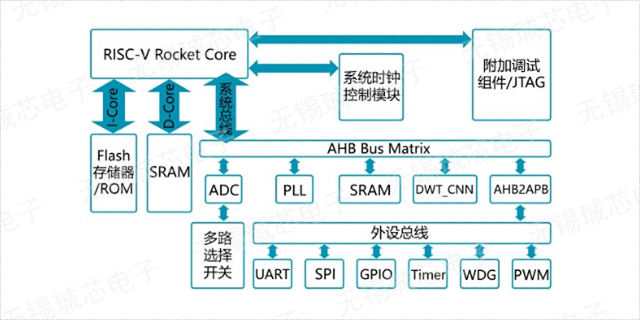

MCU的存储器MCU的存储器分为两种类型:非易失性存储器(NVM)和易失性存储器(SRAM)。NVM通常用于存储程序代码,即使在断电后也能保持数据不丢失。SRAM则用于临时存储数据,它的速度较快,但断电后数据会丢失。MCU的I/O功能输入/输出(I/O)功能是MCU与外部世界交互的关键。MCU提供多种I/O接口,如通用输入/输出(GPIO)引脚、串行通信接口(如SPI、I2C、UART)、脉冲宽度调制(PWM)输出等。这些接口使得MCU能够控制传感器、执行器和其他外部设备。北京射频芯片行业标准射频芯片是现代通信技术的组成部分,负责信号的无线传输与接收,实现各类无线通讯功能。

可测试性是确保芯片设计成功并满足质量和性能标准的关键环节。在芯片设计的早期阶段,设计师就必须将可测试性纳入考虑,以确保后续的测试工作能够高效、准确地执行。这涉及到在设计中嵌入特定的结构和接口,从而简化测试过程,提高测试的覆盖率和准确性。 首先,设计师通过引入扫描链技术,将芯片内部的触发器连接起来,形成可以进行系统级控制和观察的路径。这样,测试人员可以更容易地访问和控制芯片内部的状态,从而对芯片的功能和性能进行验证。 其次,边界扫描技术也是提高可测试性的重要手段。通过在芯片的输入/输出端口周围设计边界扫描寄存器,可以对这些端口进行隔离和测试,而不需要对整个系统进行测试,这简化了测试流程。 此外,内建自测试(BIST)技术允许芯片在运行时自行生成测试向量并进行测试,这样可以在不依赖外部测试设备的情况下,对芯片的某些部分进行测试,提高了测试的便利性和可靠性。

热管理是确保芯片可靠性的另一个关键方面。随着芯片性能的提升,热设计问题变得越来越突出。过高的温度会加速材料老化、增加故障率,甚至导致系统立即失效。设计师们通过优化芯片的热设计,如使用高效的散热材料、设计合理的散热结构和控制功耗,来确保芯片在安全的温度范围内工作。 除了上述措施,设计师们还会采用其他技术来提升芯片的可靠性,如使用高质量的材料、优化电路设计以减少电磁干扰、实施严格的设计规则检查(DRC)和布局布线(LVS)验证,以及进行的测试和验证。 在芯片的整个生命周期中,从设计、制造到应用,可靠性始终是一个持续关注的主题。设计师们需要与制造工程师、测试工程师和应用工程师紧密合作,确保从设计到产品化的每一个环节都能满足高可靠性的要求。深度了解并遵循芯片设计流程,有助于企业控制成本、提高良品率和项目成功率。

芯片运行功耗是芯片设计中的一个重要考虑因素,它直接影响到设备的电池寿命、散热需求和成本。随着芯片性能的不断提升,功耗管理变得越来越具有挑战性。设计师们采取多种策略来降低功耗,包括使用更低的电压、更高效的电路设计、动态电压频率调整(DVFS)和电源门控等技术。此外,新的制程技术如FinFET和FD-SOI也在帮助降低功耗。这些技术的应用不提高了芯片的性能,同时也使得设备更加节能,对于推动移动设备和高性能计算的发展具有重要作用。GPU芯片通过并行计算架构,提升大数据分析和科学计算的速度。湖北GPU芯片设计流程

利用经过验证的芯片设计模板,可降低设计风险,缩短上市时间,提高市场竞争力。广东网络芯片工艺

工艺节点的选择是芯片设计中一个至关重要的决策点,它直接影响到芯片的性能、功耗、成本以及终的市场竞争力。工艺节点指的是晶体管的尺寸,通常以纳米为单位,它决定了晶体管的密度和芯片上可以集成的晶体管数量。随着技术的进步,工艺节点从微米级进入到深亚微米甚至纳米级别,例如从90纳米、65纳米、45纳米、28纳米、14纳米、7纳米到新的5纳米甚至更小。 当工艺节点不断缩小时,意味着在相同的芯片面积内可以集成更多的晶体管,这不仅提升了芯片的计算能力,也使得芯片能够执行更复杂的任务。更高的晶体管集成度通常带来更高的性能,因为更多的并行处理能力和更快的数据处理速度。此外,较小的晶体管尺寸还可以减少电子在晶体管间传输的距离,从而降低功耗和提高能效比。 然而,工艺节点的缩小也带来了一系列设计挑战。随着晶体管尺寸的减小,设计师必须面对量子效应、漏电流增加、热管理问题、以及制造过程中的变异性等问题。这些挑战要求设计师采用新的材料、设计技术和制造工艺来克服。广东网络芯片工艺