人工智能的快速发展,不仅改变了我们对技术的看法,也对硬件提出了前所未有的要求。AI芯片,特别是神经网络处理器,是这一变革中的关键角色。这些芯片专门为机器学习算法设计,它们通过优化数据处理流程,大幅提升了人工智能系统的运算速度和智能水平。 AI芯片的设计考虑到了机器学习算法的独特需求,如并行处理能力和高吞吐量。与传统的CPU和GPU相比,AI芯片通常具有更多的和专门的硬件加速器,这些加速器可以高效地执行矩阵运算和卷积操作,这些都是深度学习中常见的任务。通过这些硬件,AI芯片能够以更低的能耗完成更多的计算任务。AI芯片采用定制化设计思路,适应深度神经网络模型,加速智能化进程。射频芯片设计

功耗优化是芯片设计中的另一个重要方面,尤其是在移动设备和高性能计算领域。随着技术的发展,用户对设备的性能和续航能力有着更高的要求,这就需要设计师们在保证性能的同时,尽可能降低功耗。功耗优化可以从多个层面进行。在电路设计层面,可以通过使用低功耗的逻辑门和电路结构来减少静态和动态功耗。在系统层面,可以通过动态电压频率调整(DVFS)技术,根据负载情况动态调整电源电压和时钟频率,以达到节能的目的。此外,设计师们还会使用电源门控技术,将不活跃的电路部分断电,以减少漏电流。在软件层面,可以通过优化算法和任务调度,减少对处理器的依赖,从而降低整体功耗。功耗优化是一个系统工程,需要硬件和软件的紧密配合。设计师们需要在设计初期就考虑到功耗问题,并在整个设计过程中不断优化和调整。上海射频芯片后端设计数字芯片采用先进制程工艺,实现高效能、低功耗的信号处理与控制功能。

随着芯片在各个领域的应用,其安全性问题成为公众和行业关注的焦点。芯片不仅是电子设备的,也承载着大量敏感数据,因此,确保其安全性至关重要。为了防止恶意攻击和数据泄露,芯片制造商采取了一系列的安全措施。 硬件加密技术是其中一种重要的安全措施。通过在芯片中集成加密模块,可以对数据进行实时加密处理,即使数据被非法获取,也无法被轻易解读。此外,安全启动技术也是保障芯片安全的关键手段。它确保设备在启动过程中,只加载经过验证的软件,从而防止恶意软件的植入。

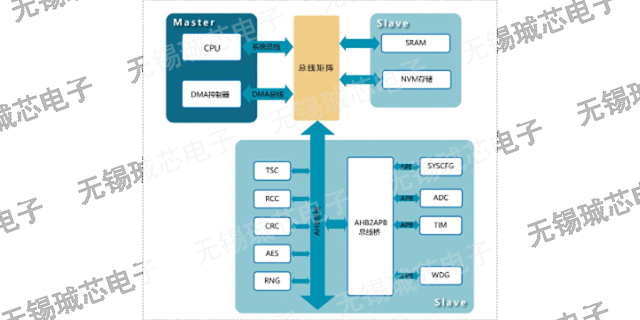

MCU的存储器MCU的存储器分为两种类型:非易失性存储器(NVM)和易失性存储器(SRAM)。NVM通常用于存储程序代码,即使在断电后也能保持数据不丢失。SRAM则用于临时存储数据,它的速度较快,但断电后数据会丢失。MCU的I/O功能输入/输出(I/O)功能是MCU与外部世界交互的关键。MCU提供多种I/O接口,如通用输入/输出(GPIO)引脚、串行通信接口(如SPI、I2C、UART)、脉冲宽度调制(PWM)输出等。这些接口使得MCU能够控制传感器、执行器和其他外部设备。数字模块物理布局的合理性,直接影响芯片能否成功应对高温、高密度封装挑战。

在芯片设计领域,优化是一项持续且复杂的过程,它贯穿了从概念到产品的整个设计周期。设计师们面临着在性能、功耗、面积和成本等多个维度之间寻求平衡的挑战。这些维度相互影响,一个方面的改进可能会对其他方面产生不利影响,因此优化工作需要精细的规划和深思熟虑的决策。 性能是芯片设计中的关键指标之一,它直接影响到芯片处理任务的能力和速度。设计师们采用高级的算法和技术,如流水线设计、并行处理和指令级并行,来提升性能。同时,时钟门控技术通过智能地关闭和开启时钟信号,减少了不必要的功耗,提高了性能与功耗的比例。 功耗优化是移动和嵌入式设备设计中的另一个重要方面,因为这些设备通常依赖电池供电。电源门控技术通过在电路的不同部分之间动态地切断电源,减少了漏电流,从而降低了整体功耗。此外,多阈值电压技术允许设计师根据电路的不同部分对功耗和性能的不同需求,使用不同的阈值电压,进一步优化功耗。设计师通过优化芯片架构和工艺,持续探索性能、成本与功耗三者间的平衡点。湖南芯片

降低芯片运行功耗的技术创新,如动态电压频率调整,有助于延长移动设备电池寿命。射频芯片设计

可测试性是确保芯片设计成功并满足质量和性能标准的关键环节。在芯片设计的早期阶段,设计师就必须将可测试性纳入考虑,以确保后续的测试工作能够高效、准确地执行。这涉及到在设计中嵌入特定的结构和接口,从而简化测试过程,提高测试的覆盖率和准确性。 首先,设计师通过引入扫描链技术,将芯片内部的触发器连接起来,形成可以进行系统级控制和观察的路径。这样,测试人员可以更容易地访问和控制芯片内部的状态,从而对芯片的功能和性能进行验证。 其次,边界扫描技术也是提高可测试性的重要手段。通过在芯片的输入/输出端口周围设计边界扫描寄存器,可以对这些端口进行隔离和测试,而不需要对整个系统进行测试,这简化了测试流程。 此外,内建自测试(BIST)技术允许芯片在运行时自行生成测试向量并进行测试,这样可以在不依赖外部测试设备的情况下,对芯片的某些部分进行测试,提高了测试的便利性和可靠性。射频芯片设计