芯片设计,是把复杂的电子系统集成到微小硅片上的技术,涵盖从构思到制造的多步骤流程。首先根据需求制定芯片规格,接着利用硬件描述语言进行逻辑设计,并通过仿真验证确保设计正确。之后进入物理设计,优化晶体管布局与连接,生成版图后进行工艺签核。芯片送往工厂生产,经过流片和严格测试方可成品。此过程结合了多种学科知识,不断推动科技发展。

芯片设计是一个高度迭代、跨学科的工程,融合了电子工程、计算机科学、物理学乃至艺术创造。每一款成功上市的芯片背后,都是无数次技术创新与优化的结果,推动着信息技术的不断前行。 射频芯片是现代通信技术的组成部分,负责信号的无线传输与接收,实现各类无线通讯功能。上海DRAM芯片IO单元库

随着芯片在各个领域的应用,其安全性问题成为公众和行业关注的焦点。芯片不仅是电子设备的,也承载着大量敏感数据,因此,确保其安全性至关重要。为了防止恶意攻击和数据泄露,芯片制造商采取了一系列的安全措施。 硬件加密技术是其中一种重要的安全措施。通过在芯片中集成加密模块,可以对数据进行实时加密处理,即使数据被非法获取,也无法被轻易解读。此外,安全启动技术也是保障芯片安全的关键手段。它确保设备在启动过程中,只加载经过验证的软件,从而防止恶意软件的植入。上海DRAM芯片时钟架构芯片设计流程是一项系统工程,从规格定义、架构设计直至流片测试步步紧扣。

可测试性是确保芯片设计成功并满足质量和性能标准的关键环节。在芯片设计的早期阶段,设计师就必须将可测试性纳入考虑,以确保后续的测试工作能够高效、准确地执行。这涉及到在设计中嵌入特定的结构和接口,从而简化测试过程,提高测试的覆盖率和准确性。 首先,设计师通过引入扫描链技术,将芯片内部的触发器连接起来,形成可以进行系统级控制和观察的路径。这样,测试人员可以更容易地访问和控制芯片内部的状态,从而对芯片的功能和性能进行验证。 其次,边界扫描技术也是提高可测试性的重要手段。通过在芯片的输入/输出端口周围设计边界扫描寄存器,可以对这些端口进行隔离和测试,而不需要对整个系统进行测试,这简化了测试流程。 此外,内建自测试(BIST)技术允许芯片在运行时自行生成测试向量并进行测试,这样可以在不依赖外部测试设备的情况下,对芯片的某些部分进行测试,提高了测试的便利性和可靠性。

除了硬件加密和安全启动,芯片制造商还在探索其他安全技术,如可信执行环境(TEE)、安全存储和访问控制等。可信执行环境提供了一个隔离的执行环境,确保敏感操作在安全的条件下进行。安全存储则用于保护密钥和其他敏感数据,防止未授权访问。访问控制则通过设置权限,限制对芯片资源的访问。 在设计阶段,芯片制造商还会采用安全编码实践和安全测试,以识别和修复潜在的安全漏洞。此外,随着供应链攻击的威胁日益增加,芯片制造商也在加强供应链安全管理,确保从设计到制造的每个环节都符合安全标准。 随着技术的发展,新的安全威胁也在不断出现。因此,芯片制造商需要持续关注安全领域的新动态,不断更新和升级安全措施。同时,也需要与软件开发商、设备制造商和终用户等各方合作,共同构建一个安全的生态系统。芯片性能指标涵盖运算速度、功耗、面积等多个维度,综合体现了芯片技术水平。

在芯片设计领域,优化是一项持续且复杂的过程,它贯穿了从概念到产品的整个设计周期。设计师们面临着在性能、功耗、面积和成本等多个维度之间寻求平衡的挑战。这些维度相互影响,一个方面的改进可能会对其他方面产生不利影响,因此优化工作需要精细的规划和深思熟虑的决策。 性能是芯片设计中的关键指标之一,它直接影响到芯片处理任务的能力和速度。设计师们采用高级的算法和技术,如流水线设计、并行处理和指令级并行,来提升性能。同时,时钟门控技术通过智能地关闭和开启时钟信号,减少了不必要的功耗,提高了性能与功耗的比例。 功耗优化是移动和嵌入式设备设计中的另一个重要方面,因为这些设备通常依赖电池供电。电源门控技术通过在电路的不同部分之间动态地切断电源,减少了漏电流,从而降低了整体功耗。此外,多阈值电压技术允许设计师根据电路的不同部分对功耗和性能的不同需求,使用不同的阈值电压,进一步优化功耗。网络芯片是构建未来智慧城市的基石,保障了万物互联的信息高速公路。广东DRAM芯片流片

GPU芯片结合虚拟现实技术,为用户营造出沉浸式的视觉体验。上海DRAM芯片IO单元库

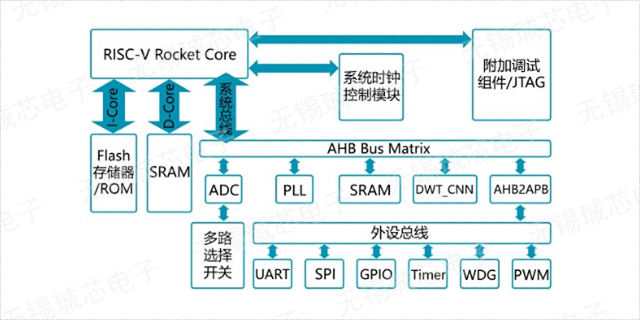

芯片设计的流程是一条精心规划的路径,它确保了从概念到成品的每一步都经过深思熟虑和精确执行。这程通常始于规格定义,这是确立芯片功能和性能要求的初始阶段。设计师们必须与市场部门、产品经理以及潜在用户紧密合作,明确芯片的用途和目标市场,从而定义出一套详尽的技术规格。 接下来是架构设计阶段,这是确立芯片整体结构和操作方式的关键步骤。在这一阶段,设计师需要决定使用何种类型的处理器、内存结构、输入/输出接口以及其他功能模块,并确定它们之间的数据流和控制流。 逻辑设计阶段紧接着架构设计,这一阶段涉及到具体的门级电路和寄存器传输级的设计。设计师们使用硬件描述语言(HDL),如VHDL或Verilog,来描述电路的行为和结构。上海DRAM芯片IO单元库