- 品牌

- YUEBO,,EPSON,,KDS,,SEIKO,NDK

- 型号

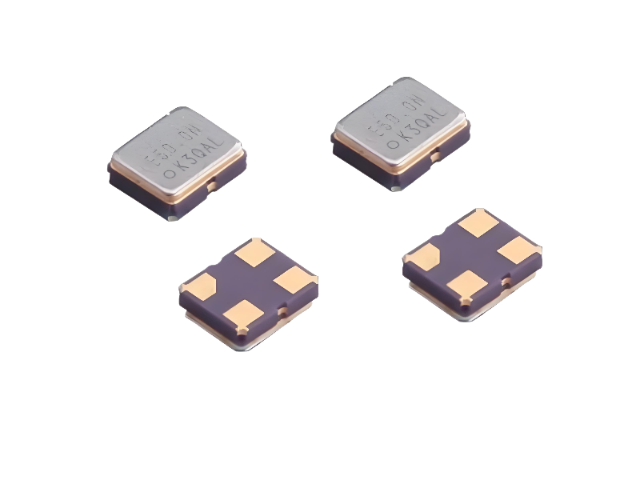

- DSB321SDN 26MHZ

- 频率特性

- 高频

- 封装材料

- 金属

- 外形

- 贴片式

- 标称频率

- 26.000

元件选型环节,无源晶振需工程师分别筛选晶振(频率、温漂)、电容(容值精度、封装)、电阻(功率、阻值)、驱动芯片(电压适配),还要验证各元件参数兼容性(如晶振负载电容与外接电容匹配),整个过程常需 1-2 天。有源晶振作为集成组件,工程师只需根据需求选择单一元件(确定频率、供电电压、封装尺寸),无需交叉验证多元件兼容性,选型时间压缩至 1-2 小时,避免因选型失误导致的后期设计调整。参数调试是传统方案很耗时的环节:无源晶振需反复测试负载电容值(如替换 20pF/22pF 电容校准频率偏差)、调整反馈电阻优化振荡稳定性,可能需 3-5 次样品打样才能达标,单调试环节就占用 1-2 周。而有源晶振出厂前已完成频率校准(偏差 ±10ppm 内)与参数优化,工程师无需进行任何调试,样品一次验证即可通过,省去反复打样与测试的时间。通信设备对频率精度要求高,适合搭配有源晶振使用。天津EPSON有源晶振生产

有源晶振能有效抵御外部干扰,关键在于其内置电路形成了 “多层干扰阻断体系”,从电源、电磁、环境温变等干扰源头进行针对性抑制,保障时钟信号纯净。首先针对电源干扰,其内置低压差稳压单元(LDO)与多层陶瓷滤波电容构成双重防护:LDO 可将外部供电的电压波动(如消费电子中电池的 3.7V-4.2V 波动)稳定在 ±0.1V 内,避免电压骤升骤降导致振荡电路参数漂移;滤波电容则能滤除供电链路中的高频纹波(如 100kHz-10MHz 的开关电源噪声),将纹波幅度抑制至 1mV 以下,防止电源噪声通过供电端侵入信号生成环节。天津EPSON有源晶振生产有源晶振助力设备快速获取时钟信号,提升研发效率。

有源晶振的环境适应性调试已内置完成。面对温度波动(如 - 40℃至 85℃工业场景),其温补模块(TCXO)或恒温模块(OCXO)已预设定补偿曲线,用户无需额外搭建温度传感器与补偿电路,也无需在不同环境下测试频率偏差并调整参数;标准化接口(如 LVDS、ECL)更省去接口适配调试,可直接对接 FPGA、MCU 等芯片。这种 “即插即用” 特性,将时钟电路调试时间从传统方案的 1-2 天缩短至几分钟,尤其降低非专业时钟设计人员的技术门槛,同时避免因调试不当导致的系统时序故障。

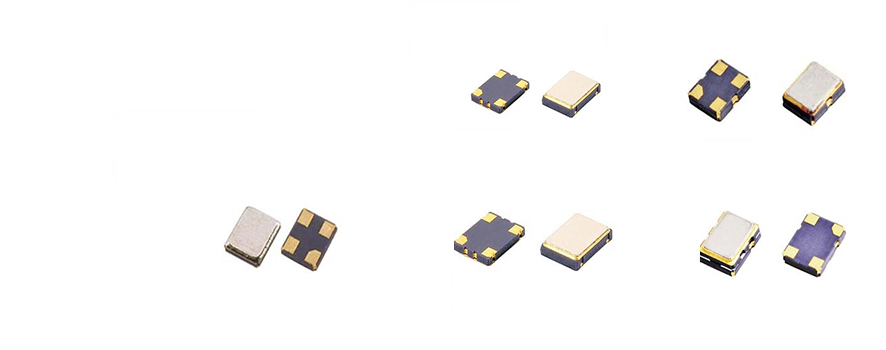

消费电子设备对简化设计的需求集中在 “空间紧凑、研发高效、成本可控” 三大维度,而有源晶振的特性恰好匹配这些诉求,成为理想选择。从空间简化来看,消费电子(如智能手机射频模块、智能手表主控单元)的内部 PCB 面积常以平方毫米计算,有源晶振通过内置振荡器、晶体管与稳压电路,可替代传统无源晶振 + 外部驱动芯片 + 阻容滤波网络的组合 —— 后者需占用 8-12mm²PCB 空间,而有源晶振采用 2.0mm×1.6mm、甚至 1.6mm×1.2mm 的微型贴片封装,单元件即可实现时钟功能,直接节省 60% 以上的空间,为电池、传感器等部件预留布局余量。有源晶振直接输出时钟信号,无需用户进行额外信号处理。

有源晶振凭借集成化与功能优化特性,从多维度降低系统复杂度、减少设计难度。首先,其内置振荡器、晶体管、稳压及滤波单元的一体化架构,省去了外部搭配元件的需求。传统无源晶振需额外设计振荡电路、放大电路与稳压模块,工程师需反复筛选 RC/LC 元件、计算电路参数以匹配频率需求,而有源晶振直接集成这些功能,可减少 30% 以上的外部元件数量,大幅简化 PCB 布局,避免因外部元件寄生参数不匹配导致的电路调试难题。其次,无需复杂驱动与校准环节。有源晶振出厂前已完成频率校准、相位噪声优化及幅度稳幅调试,输出信号直接满足电子系统时序要求。工程师无需像设计无源晶振电路那样,调试反馈电阻电容值以确保振荡稳定,也无需额外设计信号放大链路的增益补偿电路,将时钟电路设计周期缩短 50% 以上,尤其降低中小研发团队的技术门槛。有源晶振的低噪声输出,满足敏感电子设备的使用要求。武汉扬兴有源晶振批发

连接有源晶振到目标设备输入端口,即可获取稳定频率信号。天津EPSON有源晶振生产

极简接线逻辑进一步降低组装复杂度:有源晶振通常只需 2-4 个引脚即可工作(电源正、电源负、信号输出、使能端,部分简化型号只需电源与信号端),无需像无源晶振那样额外连接反馈电阻、负载电容等元件 —— 接线数量减少 60% 以上,组装时无需逐一核对多根线路的对应关系,降低对组装人员的技能要求,同时减少因接线错误导致的时钟电路故障(如漏接电容引发的频率漂移),大幅提升组装合格率,尤其适合对组装效率要求高的物联网传感器、便携医疗设备等场景。天津EPSON有源晶振生产

- 唐山EPSON有源晶振价格 2026-02-12

- 佛山TXC有源晶振应用 2026-02-08

- 广州NDK有源晶振 2026-02-08

- 武汉YXC有源晶振哪里有 2026-02-08

- 西安NDK有源晶振批发 2026-02-07

- 天津EPSON有源晶振生产 2026-02-07

- 郑州扬兴有源晶振品牌 2026-02-07

- 秦皇岛YXC有源晶振价格 2026-02-07

- 武汉KDS有源晶振价格 2026-02-06

- 河北TXC有源晶振应用 2026-02-06

- 东莞TXC有源晶振多少钱 2026-02-06

- 北京TXC有源晶振生产 2026-02-06