在多芯片、多板卡构成的复杂电子系统中,时钟信号的分配与完整性保障是重大挑战。时钟晶振作为时钟树的源头,其输出信号的驱动能力、边沿速率和信号质量直接影响下游电路。时钟晶振需要驱动可能存在的传输线损耗、时钟缓冲器的输入电容以及多个分布式负载。为此,其输出需提供符合标准(如LVCMOS、LVDS、LVPECL、HCSL)且边沿受控的波形。过缓的边沿会增加串扰和功耗,过快的边沿则易引起振铃和电磁干扰。工程师需根据负载数量、传输距离及PCB阻抗特性,选择合适的输出类型和驱动强度,并通常在输出端实施恰当的端接策略(如串联阻尼电阻)以抑制反射。良好的布局要求时钟晶振尽量靠近主芯片,并使用完整的参考平面,确保时钟信号从源头到终端都保持干净、陡峭的波形,为系统各模块提供一致的时序参考。我们的时钟晶振具有高精度和低抖动。斗门区时钟晶振时钟晶振

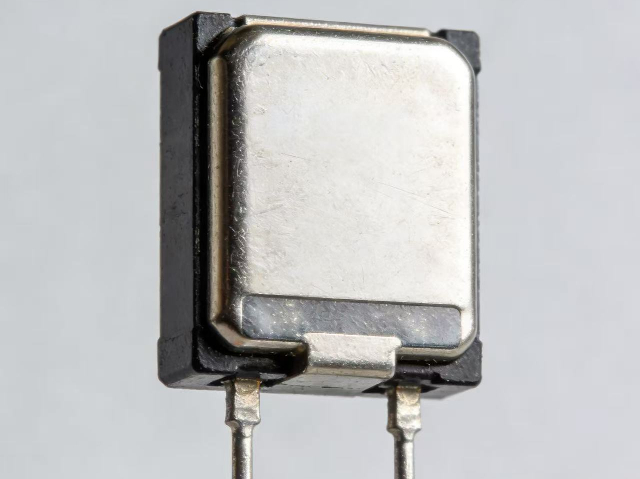

电子设备持续小型化的趋势,强力驱动着时钟晶振封装技术向微型化、高密度方向演进。从早期的全金属直插封装(如HC-49/U),到主流的表贴陶瓷封装,再到如今的芯片级尺寸封装,时钟晶振的占板面积不断缩小。3225(3.2mm x 2.5mm)、2520(2.5mm x 2.0mm)、2016(2.0mm x 1.6mm)已成为消费和通用工业领域的主流尺寸,而1612(1.6mm x 1.2mm)及更小的1008(1.0mm x 0.8mm)封装则面向可穿戴设备、超薄手机等极限空间应用。微型化封装带来了散热、密封性、抗机械应力及维持高Q值振荡等多重挑战。解决方案包括采用导热性更好的封装材料、更精密的内部结构设计、以及晶圆级封装等先进工艺。同时,将简单的时钟缓冲、电平转换或滤波功能与时钟晶振集成于单一封装的“时钟发生器”模块也日益普及,在提供稳定时钟源的同时,进一步节省了PCB空间,简化了外围电路设计。盐田区206封装时钟晶振推荐厂家鑫和顺可满足客户时钟晶振定制需求。

随着处理器内核频率和外部高速接口速率不断攀升,时钟晶振的输出频率及其谐波成分也随之进入更高频段。这对PCB上的时钟信号布线提出了严峻的高速信号完整性挑战。高频时钟信号对传输线的损耗、阻抗不连续性、串扰和反射更为敏感。设计时必须将时钟走线视为受控阻抗传输线(通常为50Ω或100Ω差分),使用合适的层叠结构,保持走线下方有完整、无分割的参考平面,并严格控制走线长度以管理传播延迟和偏斜。在时钟晶振输出端和接收端,可能需要添加串联电阻或端接电阻来匹配阻抗,减少反射。对于差分时钟(如LVDS),应确保正负走线严格等长、等间距,以保持差分信号的完整性。良好的布局布线是保证高频时钟晶振性能在PCB上得以真实再现的、也是至关重要的一环。

MEMS硅振荡器作为基于石英技术的传统时钟晶振的替代方案,凭借其半导体工艺的先天优势,在特定市场持续增长。MEMS振荡器在硅片上制造微型机械谐振器,并与CMOS振荡电路集成。其突出优点包括:极强的抗冲击与振动能力(可达数万g)、更快的启动时间(微秒级)、更宽的工作温度范围、更小的裸片级尺寸,以及与标准半导体工艺兼容带来的潜在成本与集成度优势。然而,在相位噪声、长期老化率及高频率等性能指标上,石英时钟晶振目前仍保持一定位置。市场因此呈现分层:MEMS振荡器在对耐振动、小尺寸要求高的消费电子及部分工业领域渗透较深;而石英时钟晶振则在通信基础设施、测量、航空航天等对性能有要求的领域坚守阵地。两者将在未来长期共存、竞争与互补。鑫和顺时钟晶振采用高Q值晶片。

通信基础设施,如5G基站、光传输设备、路由器与交换机,是时钟晶振的应用市场。这些设备对时钟的同步精度、相位噪声、抖动以及可靠性要求极高。在5G网络中,为了支持载波聚合、大规模MIMO和低时延业务,基站的主时钟需要极高的频率精度和低的相位噪声,以满足空口同步和信号解调的严格要求。在光传输网络中,时钟信号的抖动会被直接传递到光信号上,影响长距离传输后的信号质量。因此,通信设备通常采用高性能的温补晶振或恒温晶振作为系统主参考时钟。这些时钟晶振不仅精度高,还需支持IEEE 1588等精密时钟同步协议,或在保持模式下具备出色的短稳特性,以在网络主参考时钟暂时丢失时,维持本地时钟的稳定。时钟晶振保证系统各部分协调工作。龙华区时钟晶振时钟晶振厂家价格

鑫和顺时钟晶振经过严格老化筛选。斗门区时钟晶振时钟晶振

在系统设计中,有时会遇到电磁干扰问题,而时钟晶振及其时钟线既可能是敏感受害者,也可能是强大的干扰源。作为受害者,时钟晶振容易受到附近大功率器件(如DC-DC开关电源、电机驱动器)产生的强磁场干扰,导致输出频率出现瞬时抖动(微跳变)。因此,布局时应让时钟晶振远离这些噪声源,必要时可使用屏蔽罩。作为干扰源,时钟晶振输出的方波时钟信号富含高次谐波,这些谐波可能通过空间辐射或电源/地平面传导,干扰设备内的射频接收电路或其他敏感模拟电路。为了抑制辐射,应尽量缩短时钟线长度,并在时钟晶振电源引脚处做好滤波。使用扩频时钟晶振也是一种有效降低电磁干扰峰值的方法,其通过轻微调制时钟频率,将能量分散到一个较宽的频带上,从而降低在单一频率点的辐射强度,有助于通过EMC测试。斗门区时钟晶振时钟晶振

深圳市鑫和顺科技有限公司是一家有着先进的发展理念,先进的管理经验,在发展过程中不断完善自己,要求自己,不断创新,时刻准备着迎接更多挑战的活力公司,在广东省等地区的电子元器件中汇聚了大量的人脉以及**,在业界也收获了很多良好的评价,这些都源自于自身的努力和大家共同进步的结果,这些评价对我们而言是比较好的前进动力,也促使我们在以后的道路上保持奋发图强、一往无前的进取创新精神,努力把公司发展战略推向一个新高度,在全体员工共同努力之下,全力拼搏将共同深圳市鑫和顺科技供应和您一起携手走向更好的未来,创造更有价值的产品,我们将以更好的状态,更认真的态度,更饱满的精力去创造,去拼搏,去努力,让我们一起更好更快的成长!