- 品牌

- 云茂

- 型号

- 齐全

- 封装形式

- B***GA,CSP,QFP/PFP,MCM,SDIP,SOP/SOIC,PLCC,TSOP,TQFP,PQFP,SMD,DIP

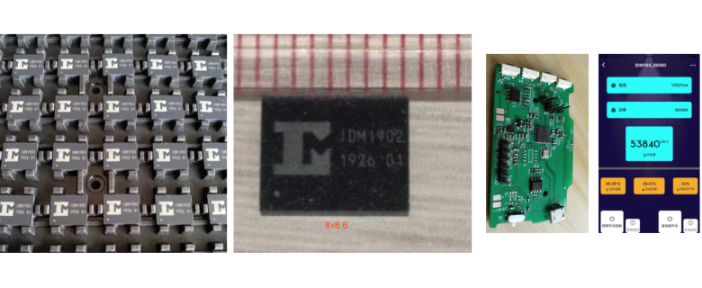

SiP系统级封装(SiP)制程关键技术,高密度打件,在高密度打件制程方面,云茂电子已达到约为婴儿发丝直径的40μm。以10x10被动组件数组做比较,大幅缩减超过70%的主板面积,其中的40%乃源自于打件技术的突破。 塑封 由于高密度打件采用微小化元器件与制程,因此元器件与载板之间的连结,吃锡量大幅减少,为提高打件可靠度,避免外界湿度、高温及压力等影响,塑封制程可将完整的元器件密封包覆在载板上。相较于一般委外封测(OSAT)塑封约100颗左右,云茂电子的系统级封装塑封技术,则是可容纳高达900颗组件。 在固晶过程中,需要对芯片施加一定的压力以确保其与基板之间的良好连接。COB封装方式

SiP 与先进封装也有区别:SiP 的关注点在于系统在封装内的实现,所以系统是其重点关注的对象,和 SiP 系统级封装对应的为单芯片封装;先进封装的关注点在于:封装技术和工艺的先进性,所以先进性的是其重点关注的对象,和先进封装对应的是传统封装。SiP 封装并无一定形态,就芯片的排列方式而言,SiP 可为多芯片模块(Multi-chipModule;MCM)的平面式 2D 封装,也可再利用 3D 封装的结构,以有效缩减封装面积;而其内部接合技术可以是单纯地打线接合(WireBonding),亦可使用覆晶接合(FlipChip),但也可二者混用。上海MEMS封装价格SIP(System In Package,系统级封装)为一种封装的概念。

SiP整体制程囊括了着晶、打线、主/被动组件SMT及塑封技术,封装成型可依据客户设计制作不同形状模块,甚至是3D立体结构,藉此可将整体尺寸缩小,预留更大空间放置电池,提供更大电力储存,延长产品使用时间,但功能更多、速度更快,因此特别适用于射频相关应用如5G毫米波模块、穿戴式装置及汽车电子等领域。微小化制程三大关键技术,在设计中元器件的数量多寡及排布间距,即是影响模块尺寸的较主要关键。要能够实现微小化,较重要的莫过于三项制程技术:塑封、屏蔽及高密度打件技术。

根据国际半导体路线组织(ITRS)的定义: SiP(System-in-package)为将多个具有不同功能的有源电子元件与可选无源器件,以及诸如MEMS或者光学器件等其他器件优先组装到一起,实现一定功能的单个标准封装件,形成一个系统或者子系统。SiP技术特点:组件集成,SiP可以包含各种类型的组件,如:数字和模拟集成电路,无源元件(电阻、电容、电感),射频(RF)组件,功率管理模块,内存芯片(如DRAM、Flash),传感器和微电机系统(MEMS)。Sip这种创新性的系统级封装不只大幅降低了PCB的使用面积,同时减少了对外围器件的依赖。

SIP工艺解析:表面打标,打标就是在封装模块的顶表面印上去不掉的、字迹清楚的字母和标识,包括制造商的信息、国家、器件代码等,主要介绍激光印码。测试,它利用测试设备(Testing Equipment)以及自动分选器(Handler),测定封装IC的电气特性,把良品、不良品区分开来;对某些产品,还要根据测试结果进行良品的分级。测试按功能可分为DC测试(直流特性)、AC测试(交流特性或timing特性)及FT测试(逻辑功能测试)三大类。同时还有一些辅助工序,如BT老化、插入、拔出、实装测试、电容充放电测试等。SiP封装技术采取多种裸芯片或模块进行排列组装。山东BGA封装厂家

SiP 兼具低成本、低功耗、高性能、小型化和多元化的优势。COB封装方式

模拟模块无法从较低的工艺集成中受益。正因为如此,并且由于试图将模拟模块保留在sperate工艺技术(BCD,BiCMOS,SiGe)上的复杂性增加,这使得SiP成为缩小系统尺寸的更具吸引力的选择。天线、MEMS 传感器、无源元件(例如:大电感器)等外部器件无法装入 SoC。因此,工程师需要使用SiP技术为客户提供完整的解决方案。交付模块而不是芯片是一种趋势,由于无线应用(如蓝牙模块)而开始,以帮助客户快速进入市场,而无需从头开始设计。相反,他们使用由整个系统组成的SiP模块。COB封装方式

无须引线框架的BGA:1、定义,LSI芯片四周引出来的像蜈蚣脚一样的端子为引线框架,而BGA(Ball Grid Array)无须这种引线框架。2、意义:① 随着LSI向高集成度、高性能不断迈进,引脚数量不断增加(如DIP与QFP等引线框架类型的封装,较大引脚数、引脚间距、切筋使用的刀片厚度与精度均达到极限);② 引线框架的引脚越小,弯曲问题就越严重,会严重妨碍后续线路板的安装,因此需要寻求不需要引线端子的封装,即BGA类型的封装(需在封装树脂底板上植球(焊锡球),以及分割封装的工序)。SiP系统级封装为设备提供了更高的性能和更低的能耗,使电子产品在紧凑设计的同时仍能实现突出的功能。浙江COB...

- 河北MEMS封装参考价 2024-12-04

- 天津模组封装 2024-12-02

- 江西SIP封装流程 2024-12-02

- 河南WLCSP封装价格 2024-12-02

- MEMS封装工艺 2024-11-30

- 陕西MEMS封装 2024-11-30

- 江西半导体芯片封装型式 2024-11-29

- 陕西IPM封装定制 2024-11-29

- 河北陶瓷封装精选厂家 2024-11-29

- 广东WLCSP封装供应 2024-11-28

- 山西WLCSP封装测试 2024-11-24

- 江苏系统级封装参考价 2024-11-23

- COB封装市价 2024-11-23

- 山东半导体芯片封装方案 2024-11-22

- 江西IPM封装 2024-11-22

- 南通WLCSP封装 2024-11-22

- 广西半导体MES系统供应商 12-04

- 上海半导体WMS系统开发商 12-04

- 天津视频监控产品方案服务 12-04

- 江苏半导体MES系统市价 12-03

- 深圳芯片设计外包管理系统开发商 12-03

- 浙江专业特种封装厂家 12-03

- 江西半导体芯片特种封装价格 12-02

- 天津模组封装 12-02

- 北京物联网电子产品方案价格 12-02

- 江西物联网电子产品方案定制价格 12-02