- 品牌

- 云茂

- 型号

- 齐全

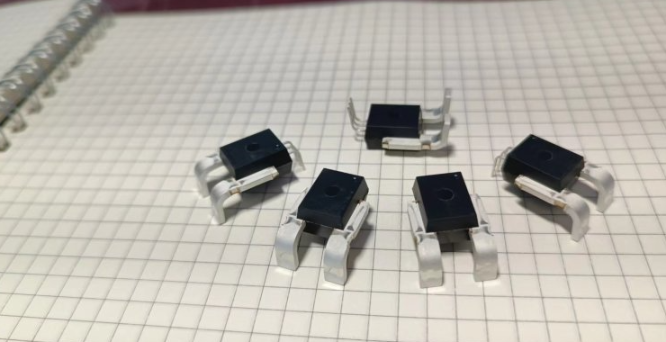

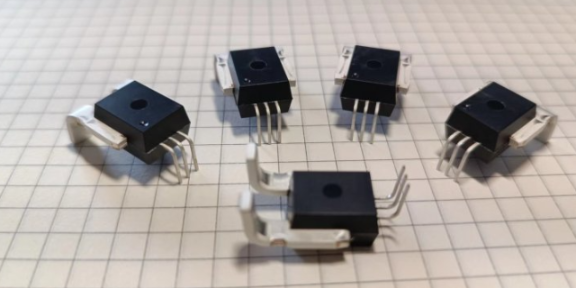

- 封装形式

- B***GA,CSP,QFP/PFP,MCM,SDIP,SOP/SOIC,PLCC,TSOP,TQFP,PQFP,SMD,DIP

Sip这种创新性的系统级封装不只大幅降低了PCB的使用面积,同时减少了对外围器件的依赖。更为重要的是,SiP系统级封装为设备提供了更高的性能和更低的能耗,使得电子产品在紧凑设计的同时仍能实现突出的功能表现。据Yole报告,2022年,SiP系统级封装市场总收入达到212亿美元。受5G、人工智能、高性能计算、自动驾驶和物联网等细分市场的异构集成、芯粒、封装尺寸和成本优化等趋势的推动,预计到2028年,SiP系统级封装市场总收入将达到338亿美元,年复合增长率为8.1%。SiP系统级封装技术将处理芯片、存储芯片、被动元件、连接器、天线等多功能器件整合在同一基板上。重庆COB封装供应商

SiP 与其他封装形式又有何区别?SiP 与 3D、Chiplet 的区别Chiplet 可以使用更可靠和更便宜的技术制造,也不需要采用同样的工艺,同时较小的硅片本身也不太容易产生制造缺陷。不同工艺制造的 Chiplet 可以通过先进封装技术集成在一起。Chiplet 可以看成是一种硬核形式的 IP,但它是以芯片的形式提供的。3D 封装就是将一颗原来需要一次性流片的大芯片,改为若干颗小面积的芯片,然后通过先进的封装工艺,即硅片层面的封装,将这些小面积的芯片组装成一颗大芯片,从而实现大芯片的功能和性能,其中采用的小面积芯片就是 Chiplet。 因此,Chiplet 可以说是封装中的单元,先进封装是由 Chiplet /Chip 组成的,3D 是先进封装的工艺手段,SiP 则指代的是完成的封装整体。通过 3D 技术,SiP 可以实现更高的系统集成度,在更小的面积内封装更多的芯片。不过,是否采用了先进封装工艺,并不是 SiP 的关注重点,SiP 关注系统在封装内的实现。辽宁COB封装工艺SIP是从封装的立场出发,对不同芯片进行并排或叠加的封装方式,实现一定功能的单个标准封装件。

什么是系统级SIP封装?系统级封装(SiP)技术是通过将多个裸片(Die)及无源器件整合在单个封装体内的集成电路封装技术。在后摩尔时代,系统级封装(SiP)技术可以帮助芯片成品增加集成度、减小体积并降低功耗。具体来说处理芯片、存储芯片、被动元件、连接器、天线等不同功能的器件,被封装在同一基板上,完成键合和加盖。系统级封装完成后提供的模块,从外观上看仍然类似一颗芯片,却实现了多颗芯片联合的功能。因此可以大幅降低PCB使用面积和对外围器件的依赖,也为设备提供更高的性能与更低的能耗。

除了2D和3D的封装结构外,另一种以多功能性基板整合组件的方式,也可纳入SiP的范围。此技术主要是将不同组件内藏于多功能基板中,亦可视为是SiP的概念,达到功能整合的目的。不同的芯片,排列方式,与不同内部结合技术搭配,使SiP 的封装形态产生多样化的组合,并可按照客户或产品的需求加以客制化或弹性生产。SiP技术路线表明,越来越多的半导体芯片和封装将彼此堆叠,以实现更深层次的3D封装。图2.19 是8芯片堆叠SiP,将现有多芯片封装结合在一个堆叠中。微晶片的减薄化是SiP增长面对的重要技术挑战。现在用于生产200mm和300mm微晶片的焊接设备可处理厚度为50um的晶片,因此允许更密集地堆叠芯片。SiP (System in Package, 系统级封装)主要应用于消费电子、无线通信、汽车电子等领域。

SiP是使用成熟的组装和互连技术,把各种集成电路器件(IC、MOS等)以及各类无源元件如电阻、电容等集成到一个封装体内,实现整机系统的功能。由于SiP电子产品向高密度集成、功能多样化、小尺寸等方向发展,传统的失效分析方法已不能完全适应当前技术发展的需要。为了满足SiP产品的失效分析,实现内部互连结构和芯片内部结构中失效点的定位,分析技术必须向高空间分辨率、高电热测试灵敏度以及高频率的方向发展。典型的SiP延用COB工艺,将电路板的主要器件塑封(COB),再把COB器件以元器件贴片到FPC软板上。SiP封装基板具有薄形化、高密度、高精度等技术特点。湖南陶瓷封装供应

SiP涉及许多类型的封装技术,如超精密表面贴装技术(SMT)、封装堆叠技术,封装嵌入式技术等。重庆COB封装供应商

SIP工艺解析:装配焊料球,目前业内采用的植球方法有两种:“锡膏”+“锡球”和“助焊膏”+“锡球”。(1)“锡膏”+“锡球”,具体做法就是先把锡膏印刷到BGA的焊盘上,再用植球机或丝网印刷在上面加上一定大小的锡球。(2)“助焊膏”+“锡球”,“助焊膏”+“锡球”是用助焊膏来代替锡膏的角色。分离,为了提高生产效率和节约材料,大多数SIP的组装工作都是以阵列组合的方式进行,在完成模塑与测试工序以后进行划分,分割成为单个的器件。划分分割主要采用冲压工艺。重庆COB封装供应商

由于物联网“智慧”设备的快速发展,业界对能够在更小的封装内实现更多功能的系统级封装 (SiP) 器件的需求高涨,这种需求将微型化趋势推向了更高的层次:使用更小的元件和更高的密度来进行组装。 无源元件尺寸已从 01005 ( 0.4 mm× 0.2 mm) 缩小到 008004( 0.25 mm×0.125 mm) ,细间距锡膏印刷对 SiP 的组装来说变得越来越有挑战性。 对使用不同助焊剂和不同颗粒尺寸锡粉的 3 种锡膏样本进行了研究; 同时通过比较使用平台和真空的板支撑系统,试验了是否可以单独使用平台支撑来获得一致性较好的印刷工艺;并比较了激光切割和电铸钢网在不同开孔尺寸下的印刷结果。SIP...

- 江西SIP封装流程 2024-12-02

- 河南WLCSP封装价格 2024-12-02

- MEMS封装工艺 2024-11-30

- 陕西MEMS封装 2024-11-30

- 江西半导体芯片封装型式 2024-11-29

- 陕西IPM封装定制 2024-11-29

- 河北陶瓷封装精选厂家 2024-11-29

- 广东WLCSP封装供应 2024-11-28

- 甘肃SIP封装技术 2024-11-28

- 北京系统级封装厂家 2024-11-26

- 北京物联网电子产品方案价格 12-02

- 江西物联网电子产品方案定制价格 12-02

- 江西SIP封装流程 12-02

- 北京特种封装参考价 12-02

- 河南WLCSP封装价格 12-02

- 广东芯片设计公司WMS系统供应商 12-01

- 湖北CP工厂EAP系统价格 12-01

- 山西防潮特种封装价格 12-01

- 江苏专业电子产品方案开发流程 12-01

- 江西防爆特种封装方案 12-01